A/D konvertori sa sukcesivnom aproksimacijom (SAR ADK)

SAR ADK imaju malu potrošnju i zauzimaju relativno malo mesta na silicijumskoj pločici. Ova kombinacija performansi ih čini idealnim za velik broj aplikacija kao što su: instrumenti koji su baterijski napajani, industrijska kontrola, akvizicija podataka i mnoge druge.

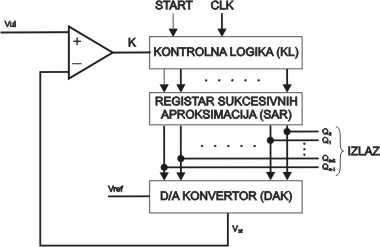

A/D konvertori sa sukcesivnim aproksimacijama su čest izbor za aplikacije sa srednjom i visokom rezolucijom i sa srednjom brzinom konverzije (od nekoliko mikrosekundi do nekoliko desetina mikrosekundi). Najčešće se biraju gde brzina odabiranja ne prelazi 5 mikrosekundi, a opseg rezolucije SAR A/D konvertora je od 8 do 16 bita. Principijelna šema A/D konvertora sa sukcesivnim aproksimacijama data je na slici 1.

Slika 1. A/D konvertor sa sukcesivnim aproksimacijama

Maksimalni ulazni napon koji se može priključiti na konvertor je Vulmax i on je jednak naponu pune skale Vps tj. Vulmax = Vps . Maksimalni izlazni napon iz D/A konvertora Viz je za 1 LSB manji od napona Vps. Pod ovakvim uslovima D/A konvertor će, kad je MSB bit postavljen na jedinicu (Qn-1 =1), a svi ostali na nulu, generisati napon Viz = Vps/ 2. Sledeći bit (Qn-2=1) ima težinu Vps / 4, odnosno, pošto se radi o binarnom D/A konvertoru, svaki sledeći bit ima težinu upola manju od predhodnog.

Konverzija počinje tako što, nakon priključenog Vul, kontrolno logičko kolo postavi logičku jedinicu u bit najveće težine registra sukcesivnih aproksimacija (Qn-1). D/A konvertor generiše napon Viz = Vps / 2 koji se poredi sa Vul. Ako je Vul > Vps / 2, MSB bit digitalnog ekvivalenta napona Vul je jedan, a ako je Vul < Vps / 2, tada taj bit treba da bude nula. Kontrolna logika, na osnovu izlaza komparatora resetuje (ako je k=0), ili ne resetuje (ako je k=1) MSB flipflop u registru sukcesivnih aproksimacija, čime je definisan bit najveće vrednosti Qn-1 izlazne informacije, a zatim postavlja drugi bit po težini Qn-2 na logičku jedinicu. Komparator poredi novu vrednost Viz (koja je Vps / 4 ili 3Vps / 4 u zavisnosti dobijenog u poređenju sa bitom najveće vrednosti) sa Vul, a zatim kontrolna logika, na osnovu izlaza komparatora resetuje ili ne flipflop za taj bit (Qn-2) i definisana je vrednost bita drugog po težini. Kontrolna logika postavlja sledeći bit koji ima težinu upola manju od predhodnog na logičku jedinicu. Proces poređenja i postavljanja narednih flipflopova se nastavlja sve do bita najmanje težine Q0. U zavisnosti od logičkog nivoa komparatora flipflop bita najmanje težine se resetuje ili ostaje logička jedinica. Time je konverzija završena.

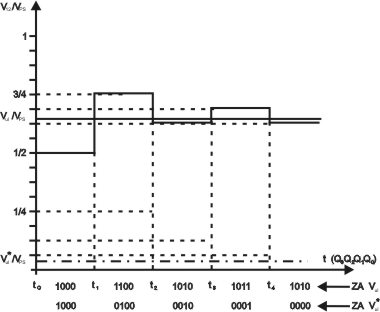

Kao primer, na slici 2. pokazan je vremenski dijagram napona Viz idealnog četvorobitnog A/D konvertora sa sukcesivnim aproksimacijama.

Slika 2. Promena napona D/A konvertora prilikom A/D konverzije

Na slici 2. je pretpostavljen ulazni napon 11/16 > Vul/Vps >5/8. Konverzija počinje postavljanjem koda “1000” u SAR (registar sukcesivnih aproksimacija). Izlazni napon D/A konvertora se postavlja na Viz = Vps / 2. Pošto je Vul > Viz, na osnovu k=1, u trenutku t1 kontrolna logika ne resetuje Q3, čime je određen MSB bit izlazne informacije, postavlja Q2=1, tako da je kod upisan u registar sukcesivnih aproksimacija (SAR) “1100”, a izlazni napon D/A konvertora se postavlja na Viz=3 / 4Vps. Sada je Vul < Viz, kontrolna logika u trenutku t2, na osnovu k=0 resetuje Q2 i bezuslovno postavlja Q1=1. Ovim je određena i druga cifra izlazne digitalne informacije. SAR je postavljen u stanje “1010”, a Viz na Viz= 5Vps/8. Pošto je Vul > Viz, k=1 zabranjuje da kontrolna logika resetuje Q1, u trenutku t3 postavlja se Q0=1, tako da je u SAR registru stanje “1011”. U trenutku t4 se na osnovu k=0 resetuje Q0, tako da je konačan rezultat konverzije koji je ostao u registru sukcesivnih aproksimacija Q3Q2Q1Q0=”1010″, što je najbliži binarni broj koji odgovara ulaznom naponu.

Na istom vremenskom dijagramu na slici 2. je isprekidanom linijom prikazan tok konverzije napona Vul < Vps / 16. Nakon četiri koraka sukcesivnih aproksimacija, kao rezultat konverzije se dobija stanje Q3Q2Q1Q0=”0000″.

Na osnovu sprovedene analize funkcionisnja A/D konvertora sa sukcesivnim aproksimacijama (skraćeno SAR ADK) mogu se definisati uslovi za sintezu registra sukcesivnih aproksimacija (SAR) i kontrolne logike (KL):

- Konverzija analognog signala u digitalni binarni kodovan broj od n cifara se obavlja u n+1 taktnom intervalu, od kojih prvi (t0) inicijalizuje sekvencu sukcesivnih aproksimacija, a poslednji (tn) označava kraj konverzije.

- Start konverzije se zadaje asinhrono u odnosu na taktni impuls A/D konvertora.

- Vreme između dva susedna taktna impulsa treba da je dovoljno dugačko, kako bi isteklo vreme postavljanja D/A konvertora, kašnjenja kroz komparator i kašnjenja kroz kontrolnu logiku.

- Korišćeni n-bitni D/A konvertor mora imati monotono rastuću karakteristiku prenosa (diferencijalnu linearnost bolju od ą0.5 LSB).

- Flipflopovi registra sukcesivnih aproksimacija (SAR registra) treba da imaju mogućnost pojedinačnog postavljanja i resetovanja.

- Ulazni napon Vul ne sme da se menja u toku konverzije, s obzirom da se flipflopovi postavljaju bit po bit, a već postavljeni flipflopovi, u slučaju promene Vul, ne mogu da promene stanje.

Vreme konverzije A/D konvertora sa sukcesivnim aproksimacijama ja dato izrazom:

gde je n- broj bita konvertora , a Tc – perioda ponavljanja impulsa CLK. Minimalna perioda ponavljanja CLK zavisi od vremena postavljanja D/A konvertora, od kašnjenja kroz komparator i kašnjenja kroz registar sukcesivnih aproksimacija sa pripadajućim logičkim kolima. Dominantan uticaj na vreme konverzije ima vreme postavljanja D/A konvertora, pošto je ovo vreme često i za red veličine duže od ostalih kašnjenja u mreži. Tipično vreme konverzije za, na primer, dvanaestobitne integrisane SAR ADK je od 1mikrosekundu za najbrže, do nekoliko desetina mikrosekundi za sporije ADK.

Brzina SAR ADK je ograničena sa:

- Vremenom smirivanja D/A konvertora

- Komparatorom, koji za određeno vreme mora da detektuje male razlike između napona Vul i Viz

- Vremenom izvršavanja logičkih operacija.

Maksimalno smirivanje D/A konvertora je najčešće određeno smirivanjem MSB-a. Linearnost celokupnog A/D konvertora je limitirana linearnošću D/A konvertora. Zbog toga, SAR ADK-i čija rezolucija prelazi 12 bita često zahtevaju neku vrstu kalibracije ili dodavanje novih komponenti da bi se postigla potrebna linearnost. Dodavanje novih komponenti donosi sa sobom i problem slaganja (uparenosti) komponenti. Zbog svega navedenog, u praksi najčešće srećemo realizacije čija rezolucija ne prelazi 12 bita.

Najvažnije prednosti A/D konvertora sa sukcesivnim aproksimacijama su mala potrošnja, visoka rezolucija, tačnost i to što zauzimaju malo mesta na silicijumskoj pločici. Glavna ograničenja u strukturi su mala brzina odabiranja, kao i zahtevi da tačnost pojedinih delova (kao što su D/A konvertor i komparator) bude na nivou tačnosti celog sistema.

Leave your response!

You must be logged in to post a comment.